在近期舉行的CadenceLive年度用戶大會(huì)中,一個(gè)核心議題引發(fā)了與會(huì)工程師、研究者與產(chǎn)業(yè)領(lǐng)袖的廣泛共鳴:在人工智能浪潮席卷全球的當(dāng)下,如何借助先進(jìn)的計(jì)算軟件工具,系統(tǒng)性、高效率地完成從底層智能芯片設(shè)計(jì)到上層AI應(yīng)用軟件開發(fā)的完整流程,從而加速智能系統(tǒng)的創(chuàng)新與落地。

一、 挑戰(zhàn):AI系統(tǒng)設(shè)計(jì)的復(fù)雜性與“墻”

傳統(tǒng)電子系統(tǒng)設(shè)計(jì)已面臨摩爾定律放緩、設(shè)計(jì)規(guī)模指數(shù)級(jí)增長等挑戰(zhàn)。而AI時(shí)代引入了新的維度:算法、硬件架構(gòu)與軟件棧必須深度融合。開發(fā)者面臨多堵“墻”:

- 算法與硬件的鴻溝:創(chuàng)新的神經(jīng)網(wǎng)絡(luò)模型(如Transformer、擴(kuò)散模型)需要特定的計(jì)算單元(如矩陣乘法單元、稀疏計(jì)算加速)和內(nèi)存層次結(jié)構(gòu)來高效執(zhí)行。手動(dòng)進(jìn)行硬件-算法協(xié)同優(yōu)化耗時(shí)且易錯(cuò)。

- 系統(tǒng)級(jí)驗(yàn)證的復(fù)雜性:智能SoC集成了異構(gòu)計(jì)算核心、高速互連、定制加速器及復(fù)雜電源管理,其功能、性能、功耗及可靠性的驗(yàn)證難度呈爆炸式增長。

- 軟件開發(fā)的滯后:底層硬件的變化要求驅(qū)動(dòng)、編譯器、算子庫乃至應(yīng)用框架的同步適配,軟件開發(fā)往往成為產(chǎn)品上市的瓶頸。

二、 破局:計(jì)算軟件的全棧賦能

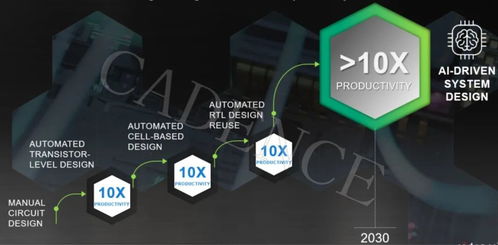

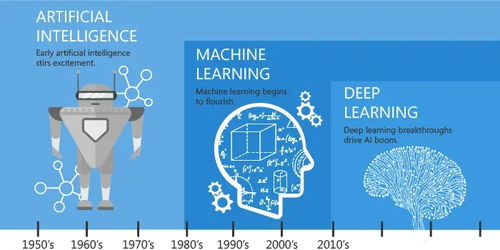

Cadence等EDA(電子設(shè)計(jì)自動(dòng)化)與計(jì)算軟件領(lǐng)導(dǎo)者提出的解決方案,正從傳統(tǒng)芯片設(shè)計(jì)向更廣泛的計(jì)算系統(tǒng)設(shè)計(jì)演進(jìn),核心在于提供全棧式、數(shù)據(jù)驅(qū)動(dòng)、高度集成的軟件平臺(tái)。

1. 智能芯片與系統(tǒng)設(shè)計(jì)加速

- AI增強(qiáng)的設(shè)計(jì)工具:利用機(jī)器學(xué)習(xí)優(yōu)化布局布線、功耗分析、時(shí)序收斂等環(huán)節(jié),大幅縮短設(shè)計(jì)周期。例如,通過預(yù)測性模型快速探索設(shè)計(jì)空間,找到功耗、性能、面積(PPA)的最優(yōu)解。

- 系統(tǒng)分析與驗(yàn)證平臺(tái):提供從架構(gòu)探索(如基于虛擬原型的性能建模)、軟硬件協(xié)同仿真到硅后驗(yàn)證的全套工具。AI技術(shù)被用于加速驗(yàn)證收斂,如智能測試生成、故障預(yù)測和覆蓋率分析。

- 專用IP與加速器設(shè)計(jì):提供經(jīng)過驗(yàn)證的AI/ML處理器IP、高速接口IP以及加速器設(shè)計(jì)環(huán)境,幫助客戶快速集成或定制專用計(jì)算單元。

2. 驅(qū)動(dòng)AI應(yīng)用軟件開發(fā)

這是本次回顧的重點(diǎn)突破方向。計(jì)算軟件的作用已不止于硬件誕生之后,而是前置并貫穿整個(gè)流程:

- 早期軟件啟動(dòng)與原型開發(fā):在硬件RTL代碼完成甚至流片之前,利用高性能硬件仿真和原型驗(yàn)證系統(tǒng),為軟件開發(fā)人員提供一個(gè)高精度、可編程的“虛擬硬件”環(huán)境。AI應(yīng)用開發(fā)者可以在此平臺(tái)上提前進(jìn)行操作系統(tǒng)移植、驅(qū)動(dòng)開發(fā)、算法部署和性能剖析,實(shí)現(xiàn)“軟硬件并行開發(fā)”,將軟件開發(fā)時(shí)間提前數(shù)月。

- 高效的算法移植與優(yōu)化:工具鏈提供從主流AI框架(如TensorFlow, PyTorch)到目標(biāo)硬件(CPU、GPU、NPU、定制加速器)的編譯優(yōu)化流程。包括自動(dòng)算子融合、圖優(yōu)化、量化感知訓(xùn)練及混合精度部署,最大化利用硬件算力,簡化開發(fā)者工作。

- 系統(tǒng)級(jí)性能與功耗分析:在統(tǒng)一的數(shù)據(jù)模型下,軟件運(yùn)行時(shí)的性能瓶頸、緩存行為、功耗熱點(diǎn)可以與底層硬件設(shè)計(jì)數(shù)據(jù)關(guān)聯(lián)分析。這使得軟件優(yōu)化不再是“黑盒”,開發(fā)者能清晰地看到代碼如何與硬件互動(dòng),從而進(jìn)行針對性優(yōu)化。

三、 未來展望:構(gòu)建自我優(yōu)化的智能系統(tǒng)

演講與討論進(jìn)一步展望了下一代趨勢:自主設(shè)計(jì)系統(tǒng)。通過將AI深度融入設(shè)計(jì)流程本身,形成閉環(huán):系統(tǒng)在運(yùn)行中收集數(shù)據(jù)(性能、功耗、錯(cuò)誤),反饋給設(shè)計(jì)工具,工具據(jù)此自動(dòng)優(yōu)化后續(xù)設(shè)計(jì)版本或?qū)崟r(shí)調(diào)整配置。計(jì)算軟件平臺(tái)將成為這一閉環(huán)的智能中樞。

結(jié)論

CadenceLive的精彩討論揭示,在人工智能時(shí)代,計(jì)算軟件(涵蓋EDA、系統(tǒng)分析、算法開發(fā)工具)的角色已從輔助工具演變?yōu)?strong>智能系統(tǒng)創(chuàng)新的核心引擎與協(xié)同平臺(tái)。通過打破硬件與軟件之間的壁壘,提供一個(gè)從硅基石到應(yīng)用頂端的連貫、智能、數(shù)據(jù)驅(qū)動(dòng)的設(shè)計(jì)環(huán)境,企業(yè)和開發(fā)者能夠以前所未有的速度將AI的想象力轉(zhuǎn)化為現(xiàn)實(shí)中的高效、可靠的智能產(chǎn)品,從而在激烈的市場競爭中占據(jù)先機(jī)。加速智能系統(tǒng)設(shè)計(jì),本質(zhì)上是加速從“想法”到“芯片”再到“用戶體驗(yàn)”的整個(gè)價(jià)值創(chuàng)造流程。